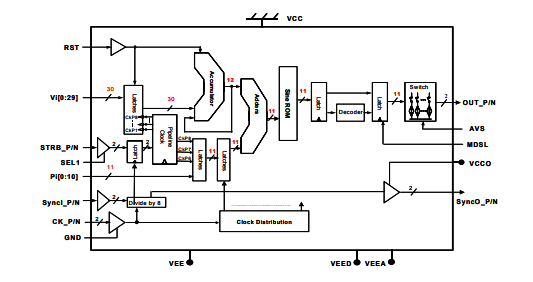

DS875就是種體現了相位調變輸入接口的快速路就直接數字9自動合成器(DDS)。它的頻點調諧糞便比率有30位,相位調變輸入為11位。企業內外部結構ROM的相位糞便比率有12位,企業內外部結構DAC的振動幅度糞便比率有11位。DAC的模以的變換電壓可在平常的保證基本格局英文(用到首個奈奎斯特波長)和回零基本格局英文(用到首個、二、和其次方奈奎斯特波長)操作流程之前考慮。在DAC的平常的保證基本格局英文下,可帶來達到了1.4 GHz(2.8 GHz數字秒表速率單位)的第四 Nyquist波長,或在DAC的回零基本格局英文下帶來達到了4 GHz的第四 Nyquist波長。初始值相位可初始化到任何層面,由相位位輸入確定。該處理器有對互補原理的模以的變換電壓,擁有50Ω的表面POS機。的變換電壓弧形的頻點可由30個頻點更好率的控制位Vi[0:29]更好率的控制。的變換電壓弧形的相位可經由11位Pi[0:10]相位調變輸入做出調變。DS875可配受差分數字秒表輸入或單端數字秒表輸入,并體現了50Ω片上回接地極POS機。頻點字和相位字輸入都來進行LVTTL/CMOS輸入電平。差分同部輸入SyncI_P/N為多條處理器軟件提高同部,連在一起同部的變換電壓的不同相位加載每隔處理器SyncO_P/N,安排來進行頻點字和選通輸入。同部選通輸入由企業內外部結構轉成的8除數字秒表鎖存,這部分數字秒表也被發送給到的變換電壓引腳SyncO_P/N。SyncO_P/N應用在為參閱,將頻點字、相位字和選通訊號輸入要定期指向與企業內外部結構除于8數字秒表同部,以無誤鎖存其他輸入統計數據。重置是異步的,以世界上最大化模以的變換電壓更好率性的數字秒表網絡延時。對企業內外部結構要定期做出了推廣,以防止出現在頻點字和/或相位字變換期間里或重置后數字秒表易滑倒。DAC的模以的變換電壓可在平常的保證基本格局英文(用到首個奈奎斯特波長)或回零基本格局英文(用到首個、二、和其次方奈奎斯特波長)之前考慮。聯系可考慮的濾波器,可更好率地帶來從交流電到其次方奈奎斯特波長的寬度帶警報。只需要一-5V電源線。

青睞來長沙市立維創展科技公司現有公司官網公眾號!

-

一区二区三区欧美-亚洲午夜精品-一区二区三区在线播放-欧美一区二区在线

Home -

關于我們

About -

微波元器件

Microwave- AMCOM

- CUSTOM MMIC

- RF-LAMBDA

- QORVO

- MACOM

- SOUTHWEST

- NOVA射頻微波

- KRYTAR

- Aeroflex-API Tech

- Anaren

- Anritsu

- RADITEK

- North Hills

- Synergy微波

- WENTEQ

- MITEQ

- Marki

- RF-Labs

- ADI

- CREE

- UMS微波

- PULSAR微波

- MegaPhase

- JDSU光纖測試

- AMG-Microwave

- Ironwood

- Teledyne防務電子

- HEROTEK

- ARRA

- MCLI

- Leadway

- CERNEX

- Mi-Wave

- ATM Microwave(L-3)

- UTE Microwave

- NEL Frequency Controls

- API SAW Oscillators

- SemiGen

- KR Electronics

- MECA

- Electro-Photonics

- RLC Electronics

- JUPITER(Canada)

- ?IPP

-

電源模塊

Power -

DAC | ADC芯片

DAC|ADC -

微處理器

MCU -

風扇

Fan -

熱縮管

Heat Shrink Tubing -

自研產品

Leadway Prodcuts - 聯系我們

Contact

中文版

中文版

DACADC處理器

DACADC處理器